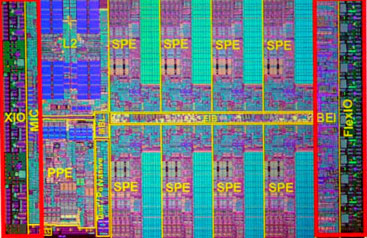

The SPEs are connected to each other and the Power PC 'brains' of the Cell by

means of an 'Element Interface Bus' (EIB); this set of four 128-bit wide data

channels also connects to the L2 cache memory and to the Memory Interface

Controller and FlexIO 'front side bus' to pass data outside the chip. The

EIB is a circular bus with two channel 'rings' traveling in opposite directions

between and through the elements of the Cell processor.

The PowerPC Processing Element

This remains a bit of a mystery, as significant details

of the operation of this processor have not yet been revealed by IBM and the

partnership. What is known is that the 'main' Cell processor is a 64-bit chip that supports dual-threaded (SMT) operation, using a 32KB L1 cache

and a 512KB level 2 cache.

Most likely, the PowerPC Processing Element (PPE)

will act as the controller, receiving, synchronizing and translating data 'jobs'

and parceling them out to one or more of the SPEs for processing. Given

that it's a powerful processor in its own right, the PPE may also lend its

muscle to the number crunching also.

Memory Interface Controller (MIC) and FlexIO:

Communicating Outside the Cell

The Memory Interface Controller connects to the EIB and

passes data to and from main memory. It's built into the die of the Cell

processor, similar to the approach taken by AMD with its 64-bit Opteron and Athlon 64 processors. The IBM MIC is connected to dual

channels of Rambus (yes that name again) XDR memory. Total bandwidth

should be in the area of 25GB/s. The Cell needs a fast memory interface to handle the data it's capable of spewing

out.

The connection between the Cell chip and the rest of the system will be

handled by the proprietary 'FlexIO' bus, providing a daunting 76.8GB/s maximum

bandwidth. This huge number is broken up considerably by the fact that the

ingoing and outgoing data handling capacity of this bus is split into two

parts; 'coherent' data traffic intended for transmission to other Cell

processors and 'non-coherent' traffic intended for the rest of the system as in

a typical 'front side bus' arrangement.