The AMB (Advanced Memory Buffer) chip is key to the

performance of FB-DIMM memory.

The AMB (Advanced Memory Buffer) chip is key to the

performance of FB-DIMM memory.

The AMB chip in each FB-DIMM module is linked to the chip in the next module

via a bi-directional serial interface. The AMB in the first memory module

connects to the memory controller on the motherboard by way of the same

high-speed serial interface. In essence, the AMB chips form a data highway that

starts at the memory controller and passes through each module in turn. The DDR2

memory DRAM chips on each FB-DIMM module load data onto this highway via the AMB

chip on the same module.

When multiple FB-DIMM memory modules occupy the same channel, each AMB acts as

a repeater for the modules 'behind' it in the signal path. Data from the

farthest modules is repeated by each closer module and daisy-chained with new

data. The AMB closest to the memory controller hosts the primary

connection and transfers all data to and from the rest of the system.

Fully buffered?

Like registered memory, FB-DIMM modules are buffered; this allows multiple

DIMMs to precisely co-ordinate data transfer for maximum stability.

Conventional registered memory only buffers the address lines, while FB-DIMM

modules buffer both address and data lines. What does this mean? It

means that every bit of data read or written from FB-DIMM memory is precisely

coordinated by the memory controller and the AMB (Advanced Memory Buffer) chip

on each module.

Potential Speed Advantages over DDR2

FB-DIMM has several built-in advantages over contemporary memory technology

which should enable it to transfer data faster standard server DDR2 RAM, even

though it is fully buffered and performs error checking.

FB-DIMM has several built-in advantages over contemporary memory technology

which should enable it to transfer data faster standard server DDR2 RAM, even

though it is fully buffered and performs error checking.

The bi-directional serial interface can send and receive data simultaneously,

which instantly eliminates the read-to-write latency associated with

conventional memory. The links themselves have a bandwidth of 3.2GB/s, 4.0GB/s or

4.8GB/s depending on the type of DDR2 memory being used in the FB-DIMM modules

(DDR2-533, 667 or 800).

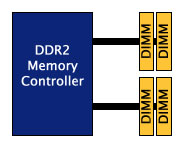

Since the serial links have a lower pin-count than conventional memory buses

and better data handling abilities, more channels can be implemented in a single

memory controller. In entry-level servers and high-end desktops, four

FB-DIMM modules, each with a channel of their own will have a considerable

bandwidth advantage over a conventional dual-channel memory controller

supporting two DDR2 DIMMS on each channel.

On the other hand, the initial latency of serial memory is said to be higher

than that of traditional memory setups, though this disadvantage disappears with

continuous transfers of data, where the inherently faster speed of the serial

memory interface and its bi-directional nature come out on top.

Potential Capacity advantages over DDR2

Capacity is where FB-DIMM really does seem to have a clear-cut advantage over

conventional memory. Since the 32-bit server should be nothing but a

memory by next year, the focus for performance is likely to shift a bit more

towards the memory as opposed to the processor(s) in any given server.

Where previously there was a hard 4GB memory limit which required some creative

(and performance sapping) memory addressing tricks to overcome, modern 64-bit

processors can potentially address effectively unlimited amounts of memory at

full speed.

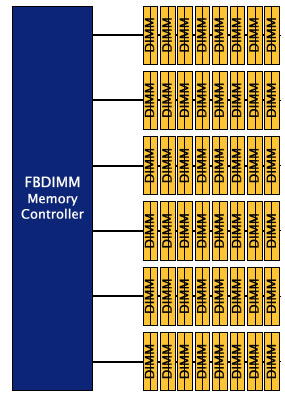

Currently, FB-DIMM technology supports up to six channels

of eight dual-layer FB-DIMM modules each. This gives a maximum of

192GB

of memory addressed by

a single memory controller!

Error checking

Similar to ECC (Error Checking and Correcting) memory, FB-DIMM modules perform

error checking and correction as well as cyclic redundancy checks on data

passing through them, thanks again to the AMB chip. The AMBs in each

memory channel co-ordinate their error checking efforts so that if a correction

or retry is necessary, all the modules stay in sync.